Esta seção continua. Sistema incorporado Outra interface de comunicação serial no protocolo de interface de comunicação de hardware - SPI 。 Comparado com o protocolo de porta serial UART, SPI Ele possui sua própria exclusividade.

O endereço é citado da seguinte forma: Http://www.eepw.com.cn/article/201812/396060.htm

breve introdução

SPI (SerialPeripheral Interface), interface periférica serial.

SPI é a abreviação de SerialPeripheral Interface. O SPI é um barramento de comunicação síncrona de alta velocidade, full duplex e ocupa apenas quatro linhas no pino do chip. Ele economiza os pinos do chip e economiza espaço e conveniência para o layout da PCB. Devido a essa característica simples e fácil de usar, mais e mais chips integraram esse protocolo de comunicação, como o AT91RM9200.

--de Enciclopédia Baidu

A interface foi desenvolvida pela Motorola em meados da década de 1980 e se tornou um padrão de fato.

--de Wiki

A partir do "padrão de fatos" consultado pela Wikipedia, podemos obter um ponto cego do conhecimento em ciências.

Padrões factuais referem-se àqueles não formulados pelas organizações de padronização, mas por empresas e grupos de negócios que estão na posição de liderança da tecnologia. Alguns deles também precisam da aprovação das organizações de aliança do setor, como os padrões de DVD que precisam ser aprovados pelo fórum do DVD e os padrões técnicos aceitos pelo mercado.

--de Enciclopédia Baidu

A interface SPI define um host e mais arquitetura de comunicação. No mesmo barramento SPI, há apenas um host e vários computadores escravos. Essa arquitetura restringe a iniciativa de comunicação apenas no lado do host, o host inicia uma comunicação e o escravo faz o desejado.

A linha de sinal

O SPI é chamado de barramento serial de quatro fios e suas linhas de sinal são:

SCLK: relógio serial (saída do host)

MOSI: saída principal da entrada escrava ou entrada escrava de saída do host (dados de saída do host).

MISO: a entrada principal da saída ou a entrada principal da saída (da saída de dados da saída).

SS: seleção de escravos (geralmente baixa eficiência, saída do host).

A nomeação das linhas de sinal também é variada.

Relógio da porta serial:

SCLK: SCK

A saída principal -> da entrada (MOSI):

SIMO, MTSR - corresponde ao MOSI entre o dispositivo principal e o dispositivo escravo.

SDI, DI, DIN, SI - do dispositivo; conecte-se ao MOSI no dispositivo principal ou conecte-se à seguinte conexão.

SDO, DO, DOUT, SO - no dispositivo principal; conecte ao MOSI da estação escrava ou conecte-se à conexão acima.

输入 <--- ---="">

SOMI, MRST - corresponde ao MISO entre o dispositivo principal e o dispositivo escravo.

SDO, DO, DOUT, SO - do dispositivo; conecte-se ao MISO no dispositivo principal ou conecte-se à seguinte conexão.

SDI, DI, DIN, SI - dispositivo principal; MISO conectado à conexão escrava ou superior.

Seleção de escravos:

SS: SSEL, CS, CE, nSS, / SS, SS #

Os nomes confusos acima são SDO, SDI, DOUT, DIN e assim por diante, e todos precisam ser vistos separadamente no equipamento principal ou apenas no equipamento. Mas, em geral, tente escrever especificações claras, o que não é fácil de criar ambiguidade.

O SPI, como interface serial síncrona, pode ser considerado como tendo dois sinais síncronos. O primeiro é selecionar sinais SS da máquina escrava, informar o escravo selecionado, preparar a comunicação SPI e o segundo é sincronizar o sinal de relógio SCLK. Quando os lados do transceptor interagem com os dados, eles são emitidos e amostrados por bit com base no salto do SCLK.

As quatro linhas de sinal não são todas necessárias, de acordo com o modo de trabalho, elas podem ser configuradas em duas e três linhas.

Na página de configuração da ferramenta STM32CubeMX, você pode ver claramente a diferença entre os pinos dos chips e os diferentes modos de operação.

A comparação constatou que a diferença entre as quatro e as três linhas do full duplex é o sinal escravo NSS. Essa situação geralmente ocorre porque o barramento SPI possui apenas uma arquitetura de comunicação principal e uma escrava, e o sinal NSS escravo sempre foi de baixo nível.

Sincronização do sinal

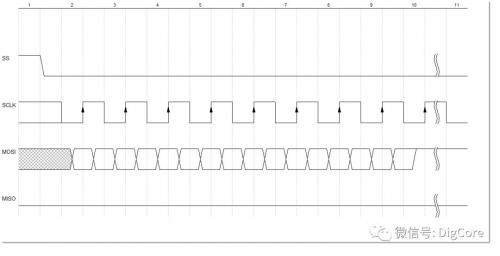

A sequência de tempo da interface SPI de quatro fios é sempre sempre baixa primeiro, selecione a linha de sinal SS da máquina, emita o SCLK e pegue os dados MOSI, neste momento o MISO é um estado de alta impedância. Do seguinte modo:

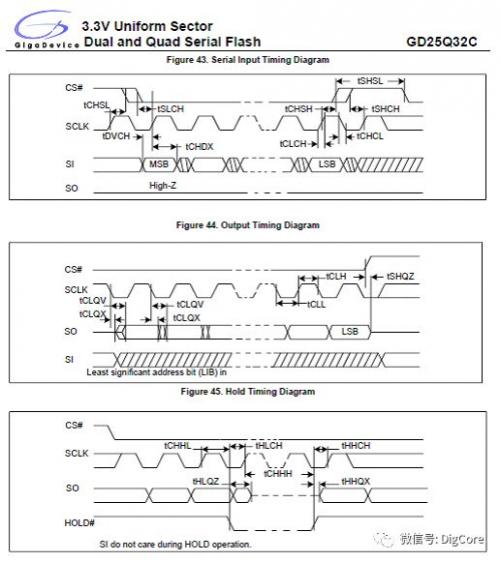

Geralmente, existem dispositivos de interface SPI e haverá diagramas de sequência correspondentes em Spec. A interface SPI é interceptada, respectivamente. O modelo FLASH é GD25Q32C, o modelo OLED da interface SPI é QG-2832TLBFG04, e as partes Spec dos dois dispositivos são introduzidas da seguinte forma: duas capturas de tela:

Não é difícil descobrir que a especificação do diagrama de temporização define a ordem e o atraso de tempo de cada nível de saída da linha de sinal e define o "alinhamento" do salto do sinal do relógio junto com o sinal de dados. O "alinhamento" aqui é na verdade a saída e a amostragem dos dados.

Da mesma forma, essa especificação de tempo especifica as características do sinal da interface SPI dos dispositivos SPI, incluindo o aumento do relógio, o tempo da borda decrescente, o atraso entre a seleção do chip e a borda de salto do relógio e a duração da borda do relógio e da linha de dados.

Essas características de tempo definem o escopo do host SPI ao se comunicar com ele ou não excedem o escopo de sua definição; caso contrário, isso levará a uma comunicação anormal a partir da resposta das peças da máquina.

Dispositivos diferentes têm requisitos de tempo diferentes para a interface SPI. O primeiro diagrama de sequência simples e, com base nesse diagrama de sequência, a interface SPI também pode configurar diferentes parâmetros de configuração da interface.

Item de configuração da interface

Em geral, a configuração opcional da interface é: modo de interface (a configuração real é a seleção de modo único e duplex), modo escravo do mestre do dispositivo, largura dos dados, polaridade do relógio (CPOL :), fase do relógio (CPHA), taxa do relógio, bit de bit de dados seleção de tamanho e terminal.

Modo de interface

A interface SPI padrão de quatro fios usa a comunicação entre o host e o escravo para interação de dados, e as duas partes têm o processo de recebimento e envio de dados. Na interface LCD / OLED SPI, ele não precisa que os dados sejam retornados ao host como o dispositivo do dispositivo. Ele só precisa receber informações de controle e exibir dados do host.

Com base nesse cenário, ele pode ser configurado como uma comunicação simplex de três fios, ou seja, apenas SS, SCLK de clock e MOSI de saída de dados podem ser selecionados na máquina.

Modo escravo mestre do dispositivo

Essa configuração geralmente precisa ver se o chip suporta ou não, e pode ser configurado como uma máquina host ou escrava SPI, para que possa ser melhor integrado ao sistema do projeto.

Largura de dados

Como o nome indica, o envio de dados pode ser configurado em 8 bits, 16 bits e assim por diante, o que também é determinado de acordo com o chip.

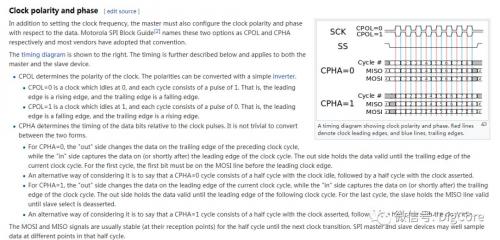

Polaridade do relógio e fase do relógio

Os dois são CPOL (Clock Polarity) e CPHA (Clock Phase). Polaridade significa alto e baixo nível. Isso define o barramento SPI no estado inativo, o relógio mantém o nível alto ou baixo, porque quando se trata de comunicação SPI, a primeira borda de salto do relógio está subindo e descendo. A fase refere-se à borda do salto do relógio, especificando a saída do sinal de dados e como a amostragem está alinhada com o relógio.

As duas configurações foram interpretadas com muita clareza na enciclopédia Wiki e Baidu.

Taxa de relógio

A seleção de taxa define a taxa de rotação da linha do sinal do relógio na transmissão de dados, que é a faixa de taxa que pode ser mantida no diagrama de sequência da interface definido por cada chip. Se a velocidade do host for definida muito rapidamente e a resposta da máquina escrava for muito lenta, a comunicação falhará.

Tamanho do bit de dados e seleção final

O bit de prioridade de envio de dados configurável, desde o primeiro protocolo UART pode saber, o bit0 de prioridade de dados especificado pelo UART0 e esse SPI é a prioridade configurável para o envio de bit, pode definir a posição mais baixa ou mais alta.

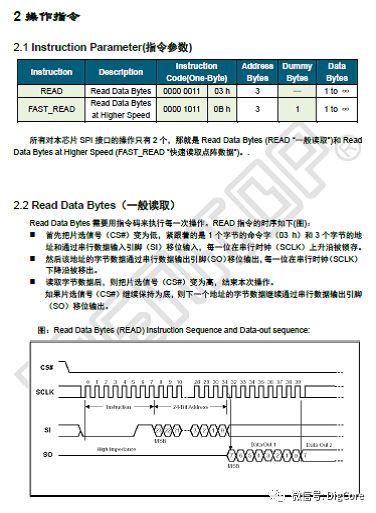

A partir das capturas de tela das séries temporais do modelo FLASH GD25Q32 e OLED QG-2832TLBFG04, podemos ver que esses dois dispositivos dão prioridade ao MSB, ou seja, a prioridade mais alta.

Em seguida, compare as instruções de um chip de fonte GT21L16S2W para leitura:

Pode-se observar que a prioridade de transmissão do MSB é comumente adotada em dispositivos SPI.

Resuma a interface de comunicação SPI, um host e arquitetura de comunicação múltipla escrava. O modo padrão possui quatro linhas de sinal, inicia a comunicação com o sinal selecionado SS, o sinal do relógio SCLK realiza saída e amostragem de bits, configurando o tempo de amostragem e priorizando o bit de emissão.